Programmable Logic Device (PLD)

PLD merupakan komponen elektronik yang dapat digunakan untuk membangun rangkaian digital sesuai dengan keinginan perancang. PLD menghubungkan beberapa gerbang logika yang diatur oleh perancang hardware. Pemrograman logika berarti bahwa desain chip baru dapat dicoba dan dapat dengan mudah diubah tanpa membutuhkan biaya untuk penyelesai- an chip dalam pabrik semikonduktor. Dengan demikian memori yang berdasarkan PLD dapat diprogram berkali – kali, yang memungkinkan produk dapat dikembangkan oleh pengguna, bukan hanya oleh pabrik saja.

Berdasarkan

jumlah gerbang logika yang dimiliki, PLD dapat dibagi atas

tiga tipe, yaitu Simple Programmable Logic Device (SPLD), Complex

Programmable Logic Device (CPLD), dan Field

Programmable Gate Array (FPGA). Dalam tulisan jejak ini lebih

dibahas tentang FPGA saja.

FIELD PROGRAMMABLE GATE ARRAY (FPGA)

Field

Programmable Logic Array (FPGA) adalah Integrated Circuit (IC)

digital yang berisi sekumpulan blok logika yang dapat dikonfigurasi.

FPGA memiliki tiga bagian

sumber daya, yaitu :

- CConfigurable Logic Blocks (CLB), sebagai blok logika merupakan blok untuk membangun komponen – komponen kombinasional / sekuensial.

- Input/Output Blocks (IOB), sebagai blok I/O merupakan blok untuk mengirimkan sinyal keluar dari chip dan sekaligus membaca sinyal yang masuk ke dalam chip.

- Programmable Switch Matrix (PSM), sebagai blok koneksi merupakan penghubung yang bisa diatur sedemikian rupa guna menghubungkan antar CLB dan CLB dengan IOB secara horizontal maupun vertikal serta memiliki kemampuan untuk mengirimkan data ke banyak sumber untuk dijadikan input. Jadi output dari CLB yang satu dapat dihubungkan ke input CLB yang lain melalui multiple PSM.

Struktur umum FPGA ditunjukkan pada Gambar

1, tetapi masing – masing vendor memiliki cara tersendiri

dalam mengatur isi dari struktur masing – masing blok. Proses pemrograman

pada FPGA dapat dilihat pada Gambar 2. Dalam proses

pemrograman tersebut terbagi kedalam beberapa tahap yaitu tahap awal

berupa design entry, functional simulation, synthesis,

implementation, timing simulation, dan device programming.

Gambar 2. Blok Diagram

Pemrograman Pada FPGA

Berikut penjelasan dari masing – masing blok diagram

pemrograman pada FPGA.

1. Design Entry

Pada bagian ini, user memulai proses perancangan rangkaian

logika yang akan diimplementasikan dalam PLD. Proses perancangan

ini dapat dikerjakan dalam dua cara yang berbeda, yaitu text entry dan schematic

entry.

Text entry, user harus

mengerti bahasa pemrograman Hardware Definition Language (HDL)

seperti VHDL atau Verilog. Sedangkan Schematic

entry merupakan cara mendesain rangkaian logika berdasarkan

rancangan schematic.

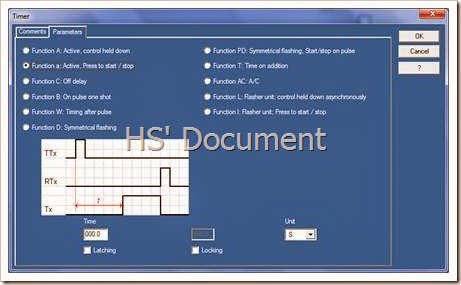

Gambar 3. Text Entry

Using VHDL

2. Functional Simulation

Tujuan dari functional simulation dalam design

flow adalah memastikan bahwa desain rangkaian logika yang dibuat

bekerja sesuai dengan keinginan user. Proses ini disimulasikan

dengan memberikan input waveforms dan

mengecek output untuk semua kemungkinan kombinasi input menggunakan waveform

editor. Selain menggunakan waveform simulator, dapat juga

menggunakan ModelSim simulator.

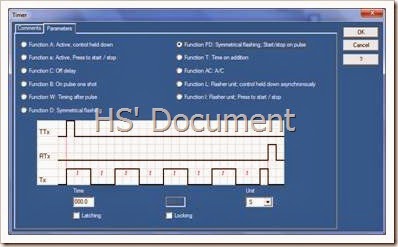

Gambar 5. Waveform

Simulator

Gambar 6. Modelsim Simulator

3. Synthesis

Pada proses ini rangkaian logika yang dibuat akan dioptimasi

dengan meminimalkan jumlah penggunaan gerbang, mengganti elemen logika dengan

elemen logika lain yang mempunyai fungsi sama, tetapi lebih efisien dalam

penggunaan gerbang, serta mengeliminasi logika yang tidak diperlukan.

Hasil terakhir dari proses synthesis adalah netlist yang

mendeskripsikan rangkaian logika yang sudah dioptimasi. Netlist adalah

daftar connection yang mendeskripsikan komponen dan bagaimana

komponen tersebut saling tersambung.

4. Implementation

Proses ini meliputi mapping, placing,

dan routing design sehingga desain tersebut dapat

diimplementasikan ke IC FPGA sesuai dengan arsitektur dan

konfigurasi pin IC FPGA tersebut. Proses implementation ini

dapat juga disebut proses fitting dimana tool fitter

CAD (Computer Aided Design) menentukan penempatan dari elemen –

elemen logic yang terdefinisi pada netlist ke

dalam elemen – elemen logic pada chip FPGA aktual.

5. Timing Simulation

Proses ini memverifikasi rangkaian tersebut bekerja dengan

frekuensi yang diinginkan dan tidak ada propagation delay atau

permasalahan waktu lain yang akan berpengaruh kepada sistem secara keseluruhan.

6. Device Programming

Proses ini akan membuat bitstream yang

merepresentasikan desain akhir. Desain akhir berupa rangkaian yang telah

dirancang diimplementasikan dalam chip FPGA oleh

pemrograman switch konfigurasi (configuration switch) yang

mengkonfigurasi elemen – elemen logic dan menetapkan sambungan

kabel yang dibutuhkan.

HARDWARE DEFINITION LANGUAGE

(HDL)

HDL merupakan bahasa pemrograman untuk hardware FPGA dimana

terdiri atas dua jenis yaitu VHSIC-HDL dan Verilog-HDL, dan jika disingkat maka

keduanya dapat dituliskan sebagai VHDL namun huruf ‘V’ pada akronim tersebut

memiliki makna yang berbeda. Kedua jenis HDL ini diimplementasikan pada tipe

FPGA yang berbeda. VHSIC-HDL diimplementasikan pada FPGA tipe Altera dengan

Quartus sebagai software engine-nya, sedangkan Verilog-HDL

diimplementasikan pada FPGA tipe Xillinc. Karena FPGA yang dimaksud dalam blog

ini adalah FPGA tipe Altera maka HDL yang dibahas adalah VHSIC-HDL.

VHSIC-HARDWARE DEFINITION

LANGUAGE (VHDL)

VHSIC merupakan kepanjangan dari Very High Speed

Integrated Circuit. Bahasa pemrograman ini telah dikembangkan oleh

departemen pertahanan dengan tujuan untuk mengembangkan suatu generasi baru

dari IC dengan kecepatan tinggi. Sebuah tim dari departemen

pertahanan telah ditugaskan untuk mengembangkan bahasa ini, dan versi pertama

telah diluncurkan pada tahun 1985. Setelah itu bahasa ini disahkan pada tahun

1987 oleh Institute of Electrical and Electronics Engineers (IEEE)

dan menjadi standar IEEE 1076-1987.

Deskripsi VHDL terdiri dari unit desain

primer dan sekunder. Unit desain primer adalah entity dan architecture,

sedangkan unit desain sekunder adalah package dan package

body. Unit desain sekunder selalu berhubungan dengan unit desain

utama. Kumpulan dari unit desain ini disimpan di dalam library.

·

Entity

Suatu entity merupakan unit desain yang

harus ada disetiap deskripsi desain VHDL. Level teratas dari desain

disebut top-level entity. Sebuah entity VHDL menunjukkan

nama entity, port entity, dan informasi lainnya yang

terkait dengan entity. Semua desain yang dibuat dapat menggunakan

satu atau lebih entity.

·

Architecture

Architecture menggambarkan

fungsi yang mendasari entity dan mengandung pernyataan model

behavior dari suatu entity. Sebuah architecture selalu

dikaitkan dengan sebuah entity dan lebih dari satu architecture per

entity dibolehkan.

·

Configuration

Configuration merupakan

daftar bagian untuk suatu desain. Deklarasi configuration sifatnya

selalu optional meskipun deskripsi desain yang dibuat sangat

kompleks.

·

Package

Sebuah package merupakan kumpulan dari jenis

data yang umum digunakan dan subprogram yang digunakan dalam desain. Hal ini

dapat dianalogikan sebagai sebuah toolbox yang berisi

beberapa tool yang digunakan untuk membangun suatu desain.

·

Process

Process adalah bagian paling dasar dalam VHDL untuk melakukan pengeksekusian. Semua deskripsi VHDL pengoperasiannya ditampilkan dalam simulasi, dan prosesnya dapat dipisahkan ke dalam satu proses atau banyak proses.